服务热线

邮箱:postmasterr@jingyeic.com

3008038871

3008038871总部地址:深圳市福田区华强北路1019号华强广场A座9H

时间:2020/7/24阅读:2324 关键词:MOS管

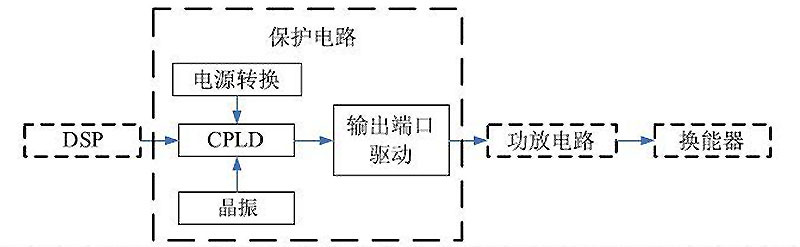

CPLD芯片保护电路

组成:电源转换 + 晶体振荡器 + CPLD + 输出端口驱动

核心:CPLD

软件:通过对电子元器件进行逻辑编程实现;

硬件:对来自DSP电路模拟输出脉冲进行信号转换和保护,对应的输出为两路驱动信号和一路包络信号;

两路输出信号:包络相同,时间同步,信号高低电平相反。

包络信号就是两路输出信号的包络,时间同步。

两路输出信号:经过光隔隔离并反相后为功率MOS管提供发射激励信号源,包络信号经光隔后为功率电路提供控制信号。

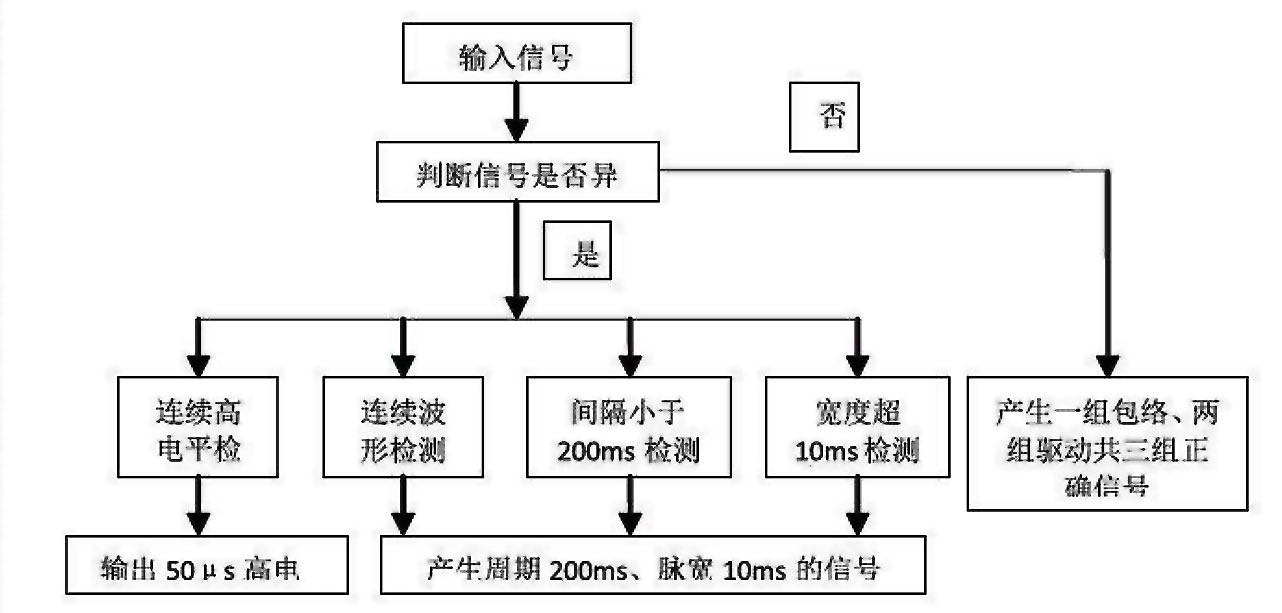

CPLD保护电路

原理:对输入MOS管电路的典型异常信号(连续波信号+短周期脉冲信号+高电平长脉冲信号)进行输入保护。

异常输入信号:连续波信号+短周期脉冲信号+高电平长脉冲信号组成;

如:连续波信号 > 10ms脉冲宽度信号

短周期脉冲信号 < 200ms脉冲周期信号

其它参数异常信号,通过简单设置软件计数器改变

保护电路软件如下图:

保护功能与时序:

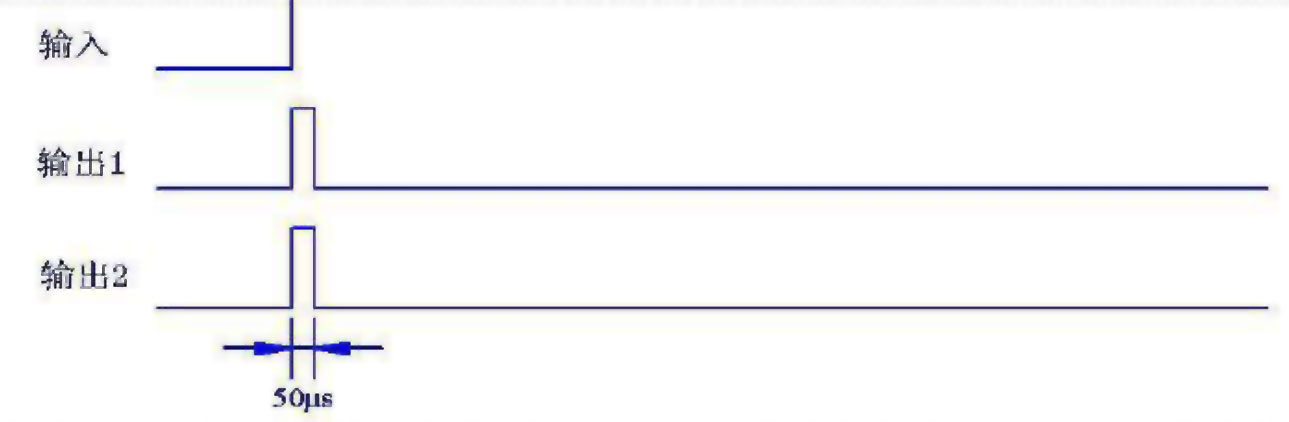

DSP电路为保护电路输入连续高电平,保护电路以第一个上升沿为基准,检测10kHz频率信号第一个周期100μs,如无下跳沿,保护输出50μs长高电平后,关闭输出端口,保持低电平。

如:DSP电路给保护电路输入连续波形信号,保护电路以第一个上升沿为基准,每隔200ms输出一个10ms的脉冲波,避免连续工作损坏功率MOS管,两路驱动信号输出和输入信号时序如下:

若输入信号两脉冲间的间隔 < 200ms,保护模块在第一个脉冲输入之后将会管制200ms的时间,保持在这200ms以内持续低电平后恢复正常。