服务热线

邮箱:postmasterr@jingyeic.com

3008038871

3008038871总部地址:深圳市福田区华强北路1019号华强广场A座9H

时间:2019/9/9阅读:5567 关键词:MOS管

上一篇列了几点MOS管会失效的原因,这一些篇我们来看看MOS管失效的解决方案。

MOS管电压失效

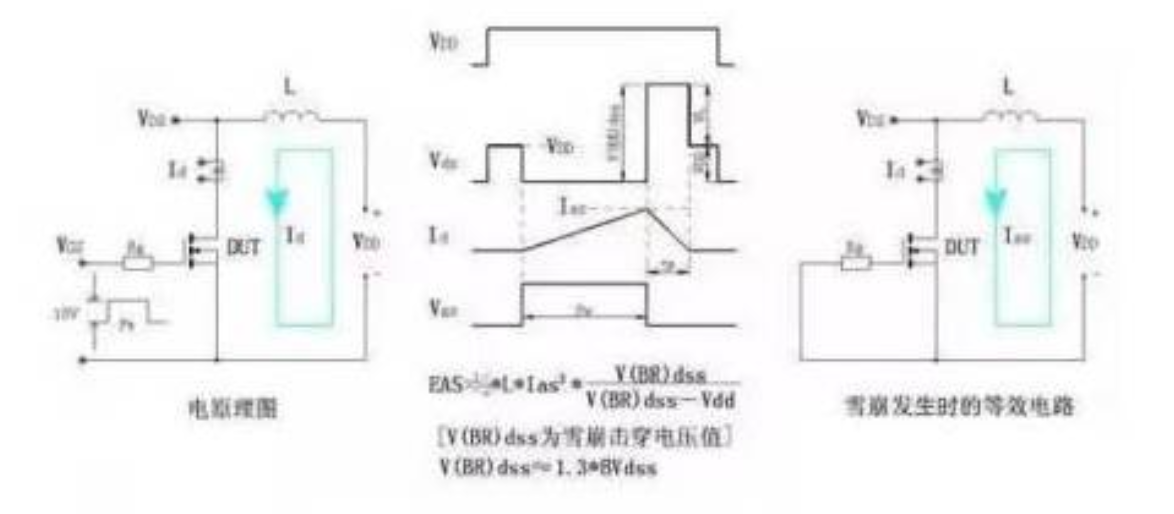

是MOSFET漏源极的电压超过其规定电压值并达到一定的能量限度,从而导致的一种失效模式。

因此我们用预防的方案来解决

1、合理降额使用,目前行业内的降额一般选取80%-95%的降额,具体情况根据企业的保修条款及电路关注点进行选取。

2、变压器反射电压的合理应用。

3、RCD和TVS合理的吸收电路设计。

4、大电流布线尽量采用粗及短的布局结构,尽量减少布线寄生电感。

5、栅极电阻Rg选择合理的产品。

6、使用大功率电源时,根据需求适当的加入RC减震或齐纳二极管进行吸收。

MOS管静电失效

静电的基本物理特征是有吸引或排斥的力量;有电场存在,与大地有电位差;会产生放电电流。这三种情形会对电子元器件造成影响:

1、元件吸附灰尘,改变线路间的阻抗,从而影响元器件功能和寿命。

2、因电场或电流破坏元器件绝缘层和导体,使元器件被完全破坏。

3、因瞬间的电场软击穿或电流产生过热,使元器件受伤,使寿命变短。

失效的预防方案:

1、MOS管电路输入端的保护二极管,它导通时电流容限一般为1mA 在可能出现过大瞬态输入电流(超过10mA)时,应串接输入保护电阻。

2、如果129#在初期设计时没有加入保护电阻,可能导致MOS管被击穿的主因,可以通过更换一个内部有保护电阻,可防止失效。

3、因保护电路吸收的瞬间能量有限,太大的瞬间信号和过高的静电电压将使保护电路失去作用。因此焊接时电烙铁必须接地,以防漏电击穿器件输入端,使用时,断电后利用电烙铁的余热进行焊接,且先焊其接地管脚。

MOS管谐振失效

1、并联功率MOS FET时未插入栅极电阻而直接连接时发生的栅极寄生振荡。

2、高速反复接通、断开漏极-源极电压时,在由栅极-漏极电容Cgd(Crss)和栅极引脚电感Lg形成的谐振电路上发生此寄生振荡。

3、当谐振条件(ωL=1/ωC)成立时,在栅极-源极间外加远远大于驱动电压Vgs(in)的振动电压,4、由于超出栅极-源极间额定电压导致栅极破坏,或者接通、断开漏极-源极间电压时的振动电压通过栅极-漏极电容Cgd和Vgs波形重叠导致正向反馈,因此可能会由于误动作引起振荡破坏。

失效预防方案:

电阻可以抑制振荡, 是阻尼的作用,可栅极串接一个小电阻, 不能解决振荡阻尼问题,最主要的是驱动电路阻抗匹配和调节功率管开关时间的因素。

MOS管栅极电压失效

栅极的异常高压来源主要有以下3种原因:

1:在生产、运输、装配过程中的静电。

2:由器件及电路寄生参数在电源系统工作时产生的高压谐振。

3:在高压冲击时,高电压通过Ggd传输到栅极

失效的预防方案:

1、栅源间的过电压保护,如果栅源间的阻抗过高,则漏源间电压突变会通过极间电容耦合到栅极,会产生很高的UGS电压过冲,因此引起栅极氧化层永久性损坏,如果是正方向的UGS瞬态电压还会导致器件的误导通。因此适当降低栅极驱动电路的阻抗,在栅源之间并接阻尼电阻或并接稳压值约20V的稳压管,并要防止栅极开路工作。

2、是漏极间的过电压防护。如果电路中有电感性负载,则当器件关断时,漏极电流的突变(di/dt)会产生比电源电压高的多的漏极电压过冲,导致器件损坏。应采取稳压管箝位,RC箝位或RC抑制电路等保护措施。

MOS管电流失效

一种是指电源在运行时异常的大电流和电压同时叠加在MOSFET上面,造成瞬时局部发热而导致的破坏模式。

另一种是芯片与散热器及封装不能及时达到热平衡导致热积累,持续的发热使温度超过氧化层限制而导致的热击穿模式。

预防方案:

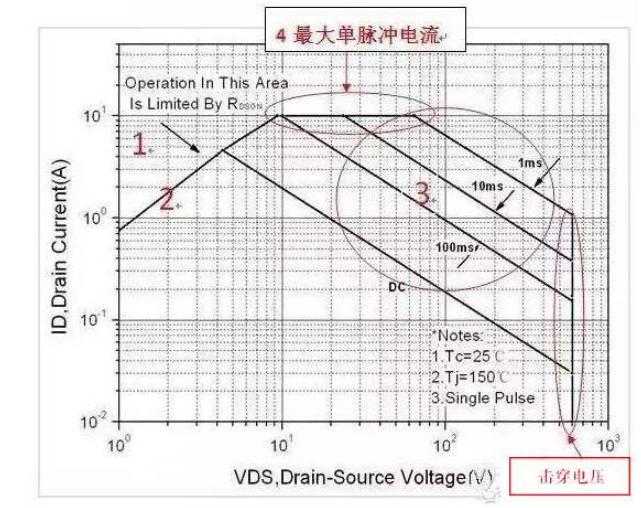

1、确保MOSFET所有功率限制条件均在SOA限制线以内。

2、将OCP功能做精确。

3、合理的热设计余量。

体二极管失效

漏源间的体二极管失效和漏源电压失效,由于二极管本身属于寄生参数,失效后难以区分躯体失效的原因,预防方案差异大,还是要看具体结合电路分析。

一般情况下失效预防方案:

MOS管的D和S本质上是对称的结构,只是沟道的两个接点。但是由于沟道的开启和关闭涉及到栅极和衬底之间的电场,那么就需要给衬底一个确定的电位。又因为MOS管只有3个管脚,所以需要把衬底接到另外两个管脚之一。那么接了衬底的管脚就是S了,没接衬底的管脚就是D,我们应用时,S的电位往往是稳定的。在集成电路中,比如CMOS中或者还有模拟开关中,由于芯片本身有电源管脚,所以那些MOS管的衬底并不和管脚接在一起,而是直接接到电源的VCC或者VEE,这时候D和S就没有任何区别了。

上一篇:IGBT离散器件电机驱动仿真工具

下一篇:场效应管在开关电源设计中的作用