服务热线

邮箱:postmasterr@jingyeic.com

3008038871

3008038871总部地址:深圳市福田区华强北路1019号华强广场A座9H

时间:2020/8/6阅读:2271 关键词:MOS管

电路功率消耗源

1.逻辑转换引起逻辑门对负载电容充电及放电功率消耗;

2.逻辑门瞬时短路电流功率消耗;

3.电子元器件漏电流消耗;

每进一次新制造技术会导致漏电流增加20倍,漏电流引起消耗是功率消耗主因。

降低功耗

1.减小电源电压

2.调整晶体管尺寸

3.并行和流水线系统结构,利用睡眠模式,采用电路;

什么是能量回收逻辑

是基于绝热计算发展起来一种低功耗设计技术;

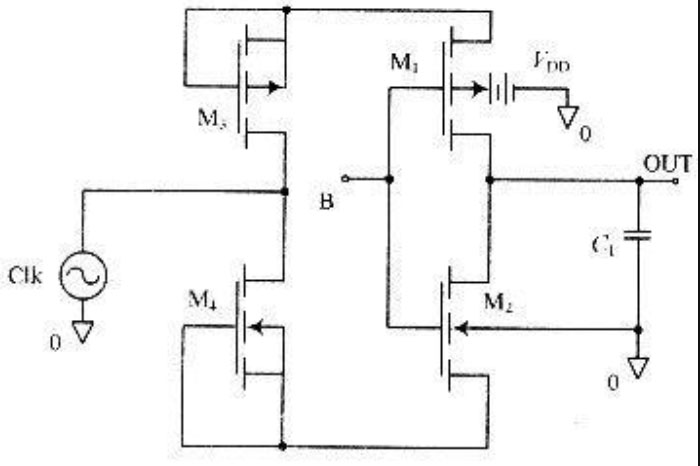

单相正弦电源时钟能量回收逻辑

用此原理电路设计一个两位数字电路,与静态CMOS数字乘法器相比,此能量回收乘法器降低功率消耗。

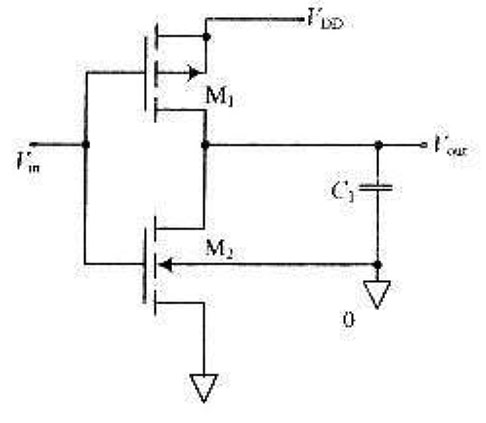

工作原理

用反相器说明电路工作原理如下图所示:

M1与M2连接方式与静态CMOS逻辑电路相似

但:电源用一个正弦信号代替,不是恒定不变,

此信号作用:同步电路工作,即电源时钟;

M3与M4连接成二极管形式

作用:控制充放电路径;

输入信号B=逻辑“O” : M1导通,M2截止。

正弦信号正半周:M3 M1向负载电容充电,电容充电到最大值,M3阻止电容向输入正弦时钟信号放电,输出保持在高电平不变。

输入信号B=逻辑“1”:M1截止,M2导通。

正弦信号负半周:负载电容通过M2和M4向输入正弦时钟信号放电,电容放电到最小值,

M4能够阻止输入正弦时钟信号向电容充电,输出保持为低电平不变。

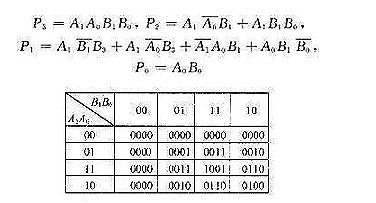

基于单相能量回收电路乘法器

两位乘法器能够实现2位二进制数乘法运算,设A1A0,B1B0为乘数和被乘数,P3P2P1P0为乘法运算得到的积,两位乘法器的输出逻辑函数表达式分别为:

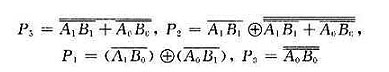

为了能用基本的与非门、或非门和异或门电路实现乘法器,上式可以通过逻辑运算变换为:

实现电路,将静态CMOS电路构成的与非门、或非门和异或门的电源时钟电路代替。

Clk+接PMOS管D极,Clk-接NMOS管S极。

静态CMOS反相器电路图如下所示:

电源时钟电路图如下所示:

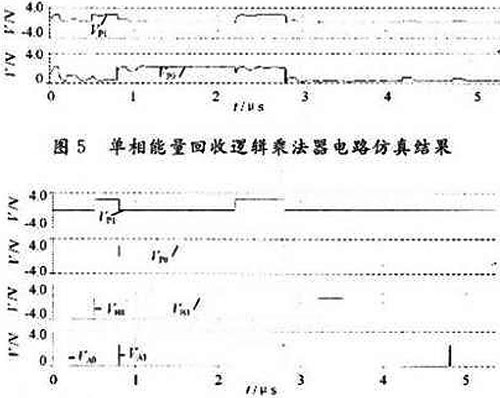

仿真结果

在PSpice环境,分别仿真用静态CMOS电路和单相能量回收电路构成的两位乘法器电路见下图所示:输出4位积低2位P1P0,输入信号 A1A0,B1B0波形如下:

采用CMOS 1.2μm技术,正弦波峰峰值=2.5 V,直流电压VDD=2.5 V,假设乘法器的输出端接负载电容=O.1 fF。

用静态CMOS电路构成乘法器输出比较稳定,输出=0或VDD,功率消耗=1.51×10-7W。

单相能量回收电路构成的二位乘法器的输出不够稳定,对噪声信号敏感,但并不影响输出逻辑,功率消耗减小为1.17×10-7W。

从节能方面,单相能量回收电路性能更好。