服务热线

邮箱:postmasterr@jingyeic.com

3008038871

3008038871总部地址:深圳市福田区华强北路1019号华强广场A座9H

时间:2021/1/4阅读:6313 关键词:MOS

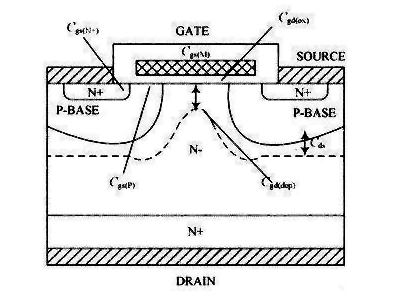

VDMOS电容和寄生电容决定其开关特性;

VDMOS电容组成:栅源电容Cgs+栅漏电容Cgd+源漏电容Cds

如下图所示

开关速度受电容充放电限制主因

栅源间电容组成

Cgs(N+)=栅源交叠电容

Cgs(M)=栅与源金属间电容

Cgs(P)=栅与P-base间电容

表达公式为:

Cgs=Cgs(N+)+Cgs(P)+Cgs(M)

它们的大小由VDMOS本身设计参数及介质层厚度决定;

Cgd由两个电容串联表达式

如下所示

1/Cgd=1/Cgd(ox)+1/Cgd(dep)

栅压未达到阈值电压,漂移区与P-base形成耗尽层结合,形成大面积耗尽层电容

其中一部份是Cgd(dep)栅下漂移区空间电荷耗尽区电容

此时,耗尽层宽度最大,耗尽电容最小;

栅极电压=阈值电压

电子元器件开启,漏区电势降低,耗尽层宽度减小,Cgd(dep)迅速增大;

漏源间电容Cds

它是一个PN结电容,元件源漏间所加电压VDS决定其大小;

VDMOS:Cgs+Cgd+Cds

功率VDMOS电容性能参考评估用Ciss+Coss+Crss

定义三个的参数如下:

输入电容Ciss=Cgs+Cgd

输出电容:Coss=Cds+Cgd

反馈电容:Crss=Cgd

以上并不是一个定值,随其外部加元件本身电压变化

td(on)=VDMOS开启延迟时间

Tr=上升时间

td(off)=关断延迟时间

Tf=下降时间

关系表达式如下

td(on)=C*issRgIn(I-Vth/Vgs)

Tr=C*issRgIn[Vgs-Vth]/[Vgs-vgs]

td(off)=C*issRgIn(Vth/vgs)

Tf=C*issRgIn(1-Vgs/Vth)

Rg=开关测试电路器件外接栅电阻

Vth=阈值电压

Vgs=外加栅源电压

Vgs=让元件漏源电压下降到外加值10%时栅源电压

考虑密勒效应C*iss=Cgs+(1+k)Cgd

由以上关系表达式,可以看出,输入电容和开关时间由Cgd直接影响,

Cgd经过密勒效应让输入电容增大,因此让元件上升时间tr和下降tf时间变大,栅漏电容Cgd减小;